编者按:本文提出了一种无电感单端转差分宽带低噪声放大器LNA,该电路包含有三个反相器结构的增益级,并且嵌有本地反馈电阻以实现宽带输入阻抗匹配的目的。而且,在第三级电路中,在电流偏置晶体管旁边并联一个电容,以改善电路增益以及差分信号的相位。基于TSMC 0.13 μm CMOS工艺进行设计,该宽带LNA在0 GHz~1.4 GHZ的频段内,取得了17.4 dB的最大增益,-5.3 dBm的最小输入三阶交调截止点IIP3,1.2 dB的最小噪声系数。该电路在1.3 V电压供电下,仅消耗了10.8 mW的功耗。

作者 / 曾渌麟 陈汶滨 西南石油大学计算机科学学院(四川 成都 610500)

本文引用地址:曾渌麟,男,汉族,1993年09月生,四川宜宾人,硕士生,研究方向:计算机无线收发前端硬件电路设计

摘要:本文提出了一种无电感单端转差分宽带低噪声放大器LNA,该电路包含有三个反相器结构的增益级,并且嵌有本地反馈电阻以实现宽带输入阻抗匹配的目的。而且,在第三级电路中,在电流偏置晶体管旁边并联一个电容,以改善电路增益以及差分信号的相位。基于TSMC 0.13 μm CMOS工艺进行设计,该宽带LNA在0 GHz~1.4 GHZ的频段内,取得了17.4 dB的最大增益,-5.3 dBm的最小输入三阶交调截止点IIP3,1.2 dB的最小噪声系数。该电路在1.3 V电压供电下,仅消耗了10.8 mW的功耗。

0 引言

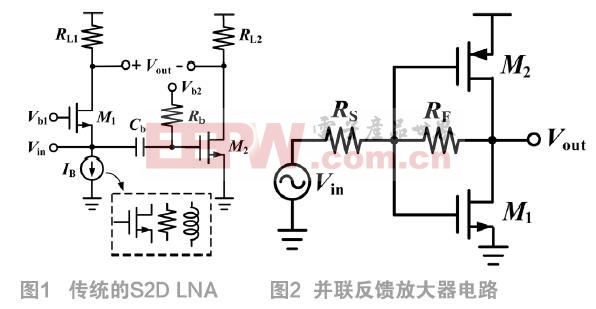

随着计算机以及960 MHz超宽带接收机系统的快速发展,并且为了降低芯片面积以及电路的复杂度,超宽带低噪声放大器LNA得到了迅猛发展。传统的无电感宽带LNA电路,例如并联反馈结构和共栅晶体管结构,并不能同时实现宽带输入匹配网络以及噪声系数的最优化[3-4]。基于共模噪声抑制以及优良的奇次谐波非线性特性的优点,差分结构得到了越来越广泛的关注,然而,LNA的前级模块天线确实单端结构,为了发挥差分电路结构的优越性,可以采用巴伦电路,但是巴伦的芯片面积过大,为了取代巴伦,出现了一种单端转差分(S2D)宽带LNA结构[5],图1所示即为传统的S2D LNA结构,电路由共源晶体管级和共栅晶体管级相级联构成,共栅晶体管级为电路提供宽带输入匹配网络。虽然共栅晶体管级引起的热噪声被差分输出结构所抑制[6],但是由电流源或偏置电阻组成的偏置电路IB会引起较大的噪声,假如采用有源器件代替,则可能会由于工艺波动问题导致偏置点的漂移。为了克服以上问题,本文提出了一款新颖的S2D宽带LNA电路,该电路可以同时实现高增益、低噪声以及宽带输入匹配网络等优良性能,并且在没有引入电感的前提下,提供差分信号的输出。

1 提出的LNA电路

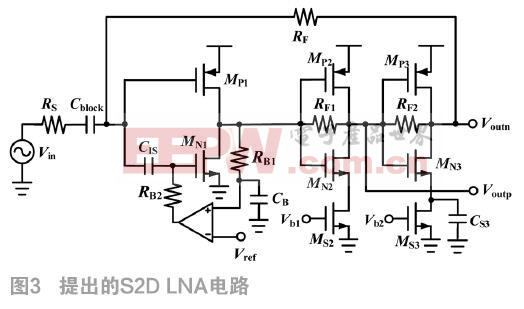

传统的并联反馈放大器电路如图2所示,该电路可以同时实现自偏置和输入阻抗匹配的目的。输入阻抗Rin可表示为:

其中,γ为MOS晶体管体效应系数,虽然,相比较无反馈结构的LNA而言,噪声系数有所改善,但是并不能同时实现输入阻抗匹配、增益以及噪声系数的最优化。

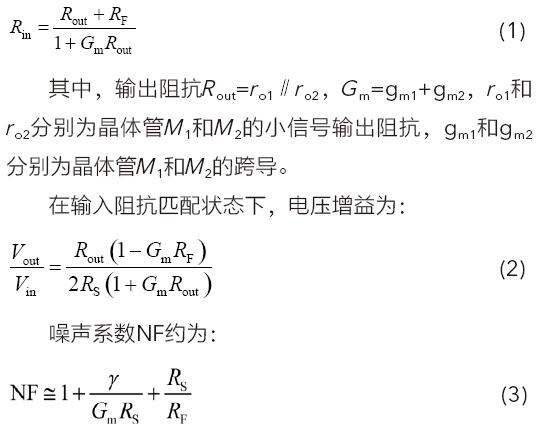

为了实现LNA性能的最优化,本文提出了一种新颖的S2D LNA电路结构,如图3所示,该电路包含有三个反相器结构的放大器电路,在后两级电路中,引入了本地反馈电阻RF1和RF2,目的是为了实现电路的自偏置,稳定直流偏置点。第一级电路引入了反馈网络,该反馈网络由RB1、RB2、RB和差分放大器组成,反馈网络的引入防止了由工艺波动所导致的输出偏置点的漂移。电容CIS用于隔离晶体管MP1和MN1的栅极偏置,优化电路偏置点[7]。

为了达到电路的高增益目标,图3所示电路的前两级需要提供足够的开环增益,第一级电路晶体管采用较大的尺寸,以提供较高的电路增益,并抑制后级电路的噪声反馈,第二级电路晶体管采用相对较小的尺寸,抑制由前级电路所导致的带宽减少问题,第三级电路起到缓冲级的作用,用以隔离下级模块对其的影响。

电容CS3并联晶体管MS3,组成RC退化网络,以改善电路增益以及差分信号的相位,退化网络的电阻ZS=roS3+1/sCS3,通过对晶体管MS3和电容CS3参数的合理选择,退化网络可为电路提供额外的增益和合适的相位延迟,并且差分结构的输出极大地改善了奇次谐波的非线性特性。每一级的电压增益A1、A2、A3和总体电压增益AV可表示为:

因为LNA的输入阻抗可由第二级电压增益A2进行调节,而噪声系数NF独立于A2,因而本文所提出的电路可通过第二级电路的调节,同时实现输入阻抗匹配和噪声系数的最优化。

2 仿真结果与分析

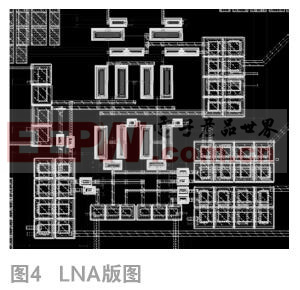

基于TSMC 0.13 μm CMOS工艺,采用Cadence软件,对本文提出的LNA进行电路设计并进行版图绘画,图4即为本文所提出的LNA电路版图,后仿真结果表明,电路在1.3 V电压供电下,消耗了10.8 mW的功耗。图5所示给出了仿真得到的S11和S22的结果,可见在整个频段内,输入反射系数S11均低于-17.5 dB,输出反射系数S22均低于-10 dB,取得了较好的输入输出匹配结果。

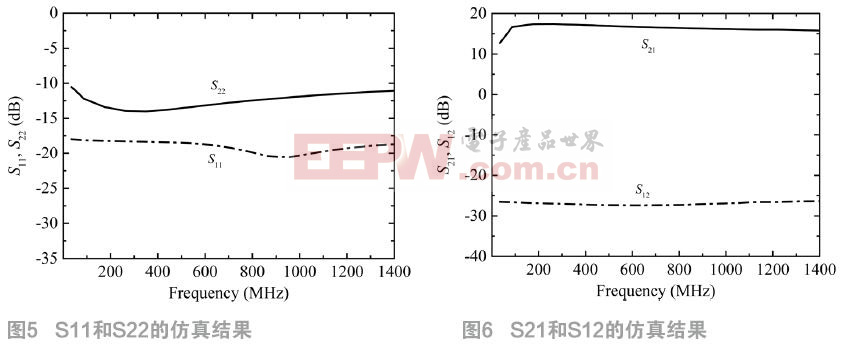

图6所示为S21和S12的仿真结果,由图可见增益S21取得了最大值为17.4 dB的数值,并且在整个频段内增益都大于12.5 dB,取得了较高的增益,隔离度S12在整个仿真频段内,均低于-25 dB,可以有效地隔离后级电路对于LNA性能的影响。

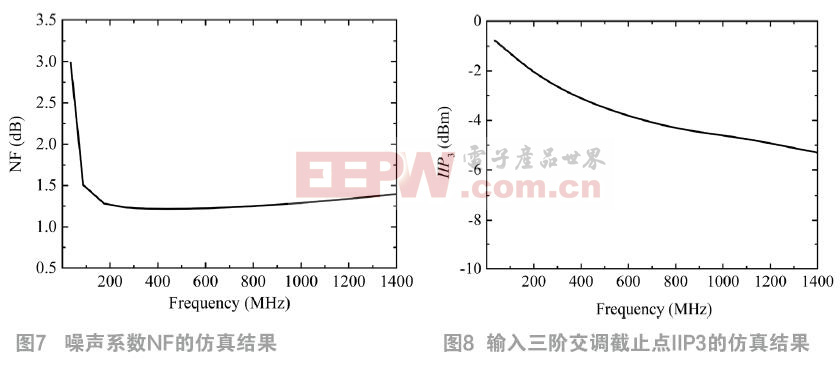

图7所示为噪声系数NF的仿真结果,取得了最低值仅为1.2 dB的优良结果,在整个频段内的噪声系数也没有达到3 dB。

图8给出了输入三阶交调截止点IIP3随着频段变化的仿真结果,在整个频段内,IIP3优于-6 dBm,并且取得了-0.78 dBm的最优值,IIP3可以通过优化电路的偏置,进一步得到改善,为了更好地验证该LNA的宽带特性,分别采用10 MHz、25 MHz和50 MHz频率间隔的双音测试法对IIP3进行仿真,IIP3的值随着频率间隔的改变并没有发生明显的变化。